# Simulation And Synthesis Techniques For Asynchronous FIFO Design

G.Kartheek<sup>1</sup>, Nageswararao.M.V<sup>2</sup>

PG scholor<sup>1</sup>ECE Department, GMRIT, Rajam, Affiliated to JNTUK University, AP, INDIA Professor<sup>2</sup>ECE Department, GMRIT, Rajam, Affiliated to JNTUK University, AP, INDIA <a href="https://linear.org/languages/languages/">languages/</a> <a href="https://linear.org/languages/">languages/</a> <a href="https://linear.org/languages/">https://linear.org/languages/</a> <a href="https://linear.o

#### **ABSTRACT**

FIFOs are frequently used to securely pass information starting with one clock space then onto the next offbeat clock area. Utilizing a FIFO to pass information starting with one clock area then onto the next clock space requires multi-nonconcurrent clock plan methods. There are numerous approaches to plan a FIFO wrong. There are numerous approaches to structure a FIFO right yet at the same t ime make it hard to appropriately combine and break down the plan. This paper will detail one strategy that is utilized to configuration, integrate and examine a protected FIFO between various clock spaces utilizing Gray code pointers that are synchronized into an alternate clock area before testing for "FIFO full" or "FIFO vacant" conditions. The completely coded, incorporated and investigated RTL Verilog model is incorporated.

Index terms-First In First Out, RTL, Test Bench

## 1. INTRODUCTION

In a RTL reproduction, if double include FIFO pointers are remembered for the structure the entirety of the FIFO pointer pieces will change at the same time; there is no way to watch synchronization and correlation issues. In a door level reproduction with no back commented on delays, there is just a slight possibility of watching an issue if the entryway advances are diverse for rising and falling edge flags, and still, at the end of the day, one would need to luck out and have the right arrangement of pieces changing only before and soon after a rising clock edge. For higher speed plans, the defer contrasts among rising and falling edge signals decreases and the likelihood of recognizing issues moreover reduces. Finding real FIFO plan issues is most noteworthy for door level structures with back commented on delays, however in any event, doing this sort of reproduction, discovering issues will be hard to do and again the chances of watching the plan issues diminishes as sign proliferation delays decrease.

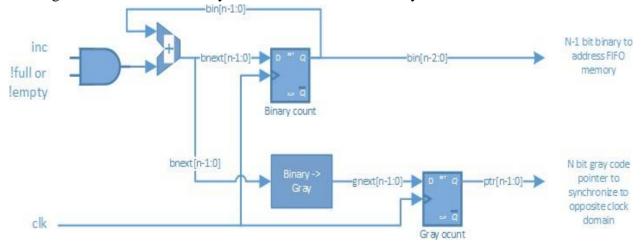

# A. Passing Multiple Asynchronous Sygnals

A 3-piece Gray code pointer is utilized to address memory and an additional piece (the MSB of a 4-piece Gray code) is added to test for full and void conditions. In the event that the FIFO is permitted to fill the initial seven areas and, at that point if the FIFO is purged by perusing back a similar seven words, the two pointers will be equivalent and will highlight address Gray-7 (the FIFO is vacant). On the following compose activity, the compose pointer will increase the 4-piece Gray code pointer (just the 3 LSBs are being utilized to address memory), making the MSBs distinctive on the 4-piece pointers yet the remainder of the compose pointer pieces will coordinate the read pointer bits, so the FIFO full banner would be attested. Not exclusively is the FIFO not full, however the 3 LSBs didn't change, which implies that the tended to memory area will over- compose the last FIFO memory area that was composed. This is one motivation behind why the double n-bit Gray code counter of Fig. 4 is utilized.

The right strategy to play out the full examination is cultivated by synchronizing the rptr into the wclk area and afterward there are three conditions that are generally essential for the FIFO to be full.

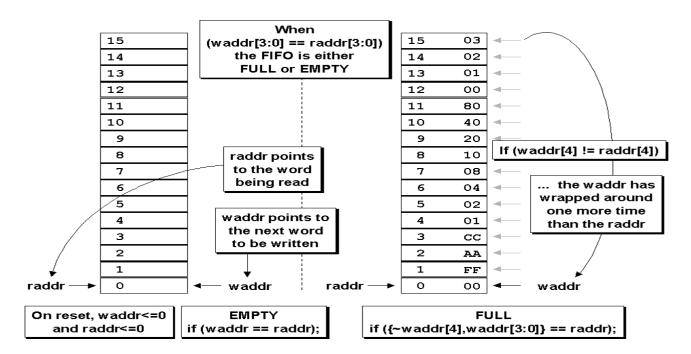

Fig. 1 FIFO Full And Empty Conditions

### B. bout FIFO

The primary reality to review a couple of grey code is that the code detachment between any 2 neighboring words is simply one (simply a small smidgeon will modification starting with one grey count then onto the following). The ensuing reality to review a couple of grey code counter is that the majority accommodating grey code counters should have force of-2 remembers for the sport set up. it's attainable to create a grey.

Code counter that counts associate degree tons variety of progressions anyway changes to and from these plans ar all things thought-about not as easy to try to to because the customary grey code. what is more note that there aren't any odd- check length grey code groupings therefore one cannot build a 23-significant grey code. this means the methodology pictured during this paper is employed to create a first in first out that's 2n vital.

- **fifo1.v** this can be the elevated level covering module that fuses all clock territories. the highest module is just used as a covering to dispatch the combination of the opposite first in first out modules employed in the arrangement. If this first in first out is employed as a locality of a bigger ASIC or FPGA set up, this elevated level covering would in all probability be discarded to allow affair of the opposite first in first out modules into their totally different clock areas for improved combine and static composing assessment.

- **fifomem.v** this can be the first in first out memory bolster that's gotten to by each the build and skim clock areas. This pad is additional doubtless than not a pink-slipped up, composed twofold port RAM. different memory designs is acclimated to fill in because the first in first out pad.

- sync\_r2w.v this can be a synchronoscope module that's accustomed synchronize the scan pointer into the shape clock zone. The synchronic scan pointer are going to be utilized by the wptr\_full

module to create the first in first out full condition. This module simply contains flip-flops that ar synchronic to the shape clock. No different justification is related to this module.

- **sync\_w2r.v** this can be a synchronoscope module that's accustomed synchronize the produce pointer into the read- clock territory. The synchronic produce pointer are going to be utilized by the rptr\_empty module to deliver the first in first out void condition. This module simply contains flipwallows that ar synchronic to the scan clock. No different justification is related to this module.

- **rptr\_empty.v** this module is totally organized to the examined clock zone and contains the first in first out scan pointer and void flag methodology of reasoning.

- wptr\_full.v this module is completely cooccurring to the build clock area and contains the first in first out produce pointer and full-flag methodology of reasoning.

## 2. THEORETICAL STUDY

# A. Handling Full & Empty Conditions

Extractly how FIFO full and FIFO void are executed is structure subordinate. The FIFO structure in this paper expect that the vacant banner will be created in the read-clock area to protect that the unfilled banner is distinguished quickly when the FIFO support is vacant, that is, the moment that the read pointer makes up for lost time to the compose pointer (counting the pointer MSBs).

The FIFO structure in this paper accept that the full banner will be produced in the compose clock area to guarantee that the full banner is recognized promptly when the FIFO cradle is full, that is, the moment that the compose pointer gets up to speed to the read pointer (aside from various pointer MSBs). So as to perform FIFO full and FIFO void tests utilizing this FIFO style, the peruse and compose pointers must be passed to the contrary clock space for pointer examination.

# **B.** Generating Empty

The FIFO is vacant when the read pointer and the synchronized compose pointer are equivalent. The vacant examination is easy to do. Pointers that are the slightest bit bigger than expected to address the FIFO memory cradle are utilized. On the off chance that the additional pieces of the two pointers (the MSBs of the pointers) are equivalent, the pointers have wrapped a similar number of times and if the remainder of the read pointer rises to the synchronized compose pointer, the FIFO is vacant.

The Gray code compose pointer must be synchronized into the read-clock space through a couple of synchronizer registers found in the sync\_w2r module. Since just the slightest bit changes one after another utilizing a Gray code pointer, there is no issue synchronizing multi-bit advances between clock spaces. So as to proficiently enroll the rempty yield, the synchronized compose pointer is really looked at against the rgraynext (the following Gray code that will be enlisted into the rptr). The vacant worth testing and the going with successive consistently square has been separated from the rptr\_empty.v code.

To change over a 4-piece to a 3-piece Gray code, we don't need the LSBs of the second 50% of the 4-piece arrangement to be a perfect representation of the LSBs of the main half, rather we need the LSBs of the subsequent half to rehash the 4-piece LSB succession of the principal half.

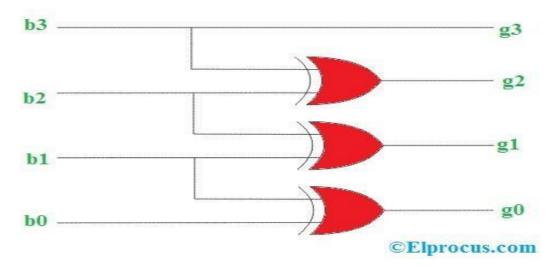

# Fig.2 3-bit Grey Code Counter

## C. Generating Full

Since the full banner is produced in the compose clock area by running a correlation between the compose and read pointers, one safe method for doing FIFO configuration necessitates that the read pointer be synchronized into the compose clock space before doing pointer examination.

The full examination isn't as easy to do as the unfilled correlation. Pointers that are the slightest bit bigger than expected to address the FIFO memory cushion are as yet utilized for the correlation, however just utilizing Gray code counters with an additional piece to do the examination isn't legitimate to decide the full condition. The issue is that a Gray code is a symmetric code aside from the MSBs.

Consider the model appeared in Fig.6 of a 8-profound FIFO. In this model, a 3-piece Gray code pointer is utilized to address memory and an additional piece (the MSB of a 4-piece Gray code) is added to test for full and void conditions. In the event that the FIFO is permitted to fill the initial seven areas (words 0-6) and afterward if the FIFO is discharged by perusing back a similar seven words, the two pointers will be equivalent and will highlight address Gray-7 (the FIFO is vacant). On the following compose activity, the compose pointer will augment the 4-piece Gray code pointer (recall, just the 3 LSBs are being utilized to address memory), making the MSBs diverse on the 4-piece pointers yet the remainder of the compose pointer pieces will coordinate the read pointer bits, so the FIFO full banner would be declared. This isn't right! Not exclusively is the FIFO not full, however the 3 LSBs didn't change, which implies that the tended to memory area will over-compose the last FIFO memory area that was composed.

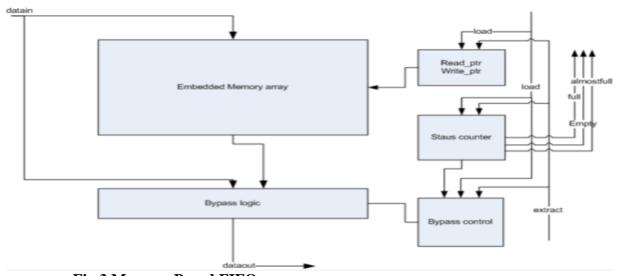

Fig.3 Memory Based FIFO

# **D. Different Clock Speeds**

Since offbeat FIFOs are timed from two diverse clock spaces, clearly the timekeepers are running at various rates. When synchronizing a quicker clock into a more slow clock space, there will be some tally esteems that are avoided because of the way that the quicker clock will semi-occasionally augment twice between more slow clock edges.

The Synchronizing multi-bit changes is just an issue when numerous pieces are changing close to the rising edge of the synchronizing clock. The way that a Gray code counter could increase twice (or more) between more slow synchronization

clock edges implies that the primary Gray code change will happen a long time before the rising edge of the more slow clock and just the subsequent Gray code progress could change close to the rising clock edge. There is no multi-bit synchronization issue with Gray code counters.

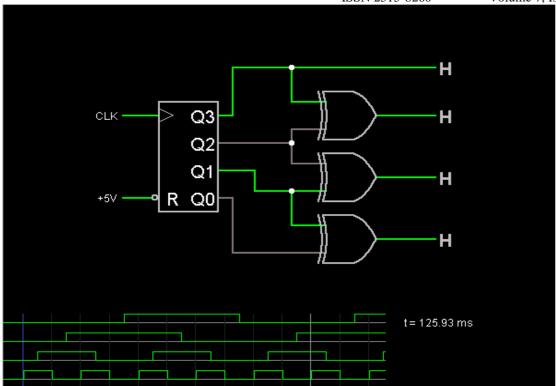

Fig.4 Dual-Clock Asychronous FIFO

The FIFO structure in this paper expect that the vacant banner will be created in the read-clock area to protect that the vacant banner is identified quickly when the FIFO cushion is vacant, that is, the moment that the read pointer gets up to speed to the compose pointer (counting the pointer MSBs).

The FIFO structure in this paper accept that the full banner will be created in the compose clock area to protect that the full banner is recognized promptly when the FIFO support is full, that is, the moment that the compose pointer gets up to speed to the read pointer (aside from various pointer MSBs).

So as to perform FIFO full and FIFO void tests utilizing this FIFO style, the peruse and compose pointers must be passed to the contrary clock area for pointer correlation.

# 3. METHODOLOGY

## A. FIFO Testing Troubles

Attempting to synchronize a twofold tally an incentive starting with one clock area then onto the next is risky in light of the fact that all of a n-bit counter can change at the same time (model 7->8 in double numbers is 0111->1000, all pieces changed). One way to deal with the issue is test and hold intermittent twofold include values in a holding register and pass a synchronized prepared sign to the new clock space. At the point when the prepared sign is perceived, the getting clock space imparts back a synchronized recognize sign to the sending clock area. An inspected pointer must not change until a recognize signal is gotten from the getting clock area. A tally an incentive with numerous changing pieces can be securely moved to another clock area utilizing this procedure. Endless supply of a recognize signal, the sending clock space has consent to clear the prepared sign and re-test the paired tally esteem.

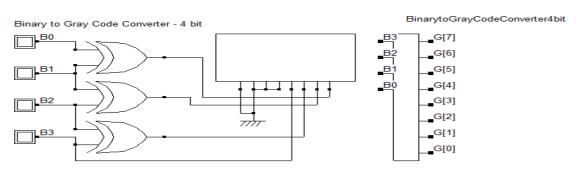

Fig.5 BCD To Grey Code Conversion

# **B.** Grey Code Counter Basics

So as to comprehend FIFO plan, one needs to see how the FIFO pointers work. The compose pointer consistently focuses to the following word to be composed; thusly, on reset, the two pointers are set to zero, which likewise happens to be the following FIFO word area to be composed. On a FIFO-compose activity, the memory area that is highlighted by the compose pointer is composed, and afterward the compose pointer is increased to highlight the following area to be composed.

Additionally, the read pointer consistently focuses to the current FIFO word to be perused. Again on reset, the two pointers are reset to zero, the FIFO is vacant and the read pointer is highlighting invalid information (in light of the fact that the FIFO is unfilled and the vacant banner is declared). When the primary information word is kept in touch with the FIFO, the compose pointer augments, the vacant banner is cleared, and the read pointer that is as yet tending to the substance of the main FIFO memory word, quickly drives that first substantial word onto the FIFO information yield port, to be perused by the beneficiary rationale. The way that the read pointer is continually highlighting the following FIFO word to be perused implies that the collector rationale doesn't need to utilize two clock periods to peruse the information word. On the off chance that the beneficiary initially needed to increase the read pointer before perusing a FIFO information word, the collector would clock once to yield the information word from the FIFO, and clock a subsequent chance to catch the information word into the recipient. That would be unnecessarily wasteful.

Fig.6 Binary To Grey Code Converter

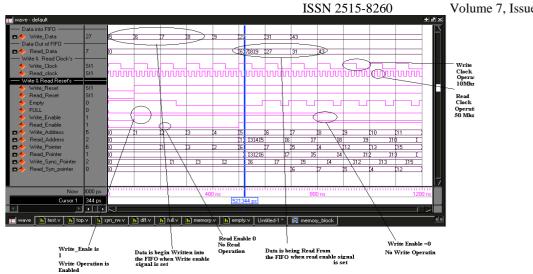

## 4. RESULTS

# A. FIFO Memory

An Asynchronous FIFO Design alludes to a FIFO Design where in the information esteems are kept in touch with the FIFO memory from one clock area and the information esteems are perused from an alternate clock space, where in the two clock areas are Asynchronous to one another. Nonconcurrent FIFO's are generally used to securely pass the information starting with one clock area then onto the next clock space.

Rationale Synthesis is the way toward changing over an elevated level depiction of the plan into a streamlined, door level portrayal, utilizing the cells in the innovation library.

Rationale Synthesis apparatus acknowledges elevated level depictions at the register move Level (RTL). What's more, an innovation library creates an enhanced door level net rundown, Translation, Logic advancement, and innovation planning are the interior procedure in a rationale amalgamation apparatus and are regularly undetectable to the client. Not all verilog develops are adequate to a rationale blend apparatus.

Fig.7 FIFO Memory Output

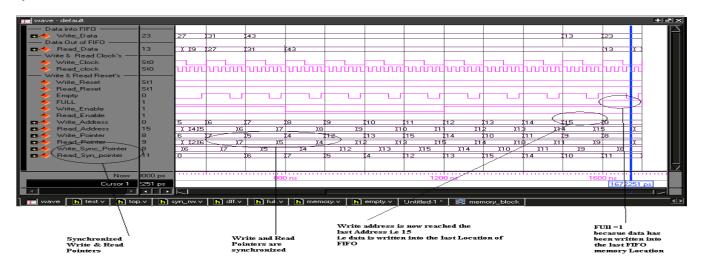

# **B. Status Signal**

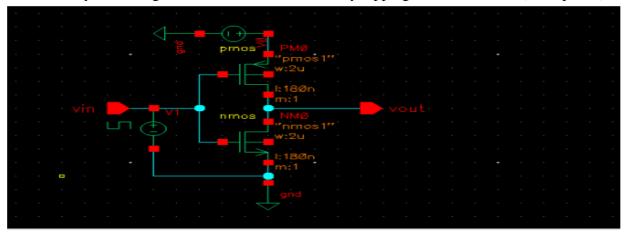

In rhythm Virtuoso the schematic circuit of the 3T-2R tcam can be executed as a mix of MOS semiconductors and resistors. At that point for the reenactment DVE L (Analog Design Environment) reproduction can be utilized.

To interface the I/O sticks now. Adding Pins To include the info and yield pins, click on the "Pin" symbol at the lower left corner. The "Include Pin" structure shows up. Under the Pin.

Fig.8 Status Signal Output

## **C.Cadence RTL Compiler**

The last schematic will resemble this as appeared in Fig.11. Check and Save your plan Then the following stage is to Check and Save the structure, either click the upper left fasten or go to Design -> Check and Save. In the "Virtuoso" CIW window if any blunders will show up. check there are no mistakes or alerts, if there are any you need to return and fix them! The Virtuoso window will give the message as demonstrated as follows. "Schematic" check finished without any blunders. "CMOS Inverter my inverter schematic" spared.

Presently in the "Virtouso Analog Artist" (Fig.11) go To interface the I/O sticks now. Adding Pins To incorporate the information and yield pins, click on the "Pin" image at the lower left corner. The "Incorporate Pin" structure appears. Under the Pin "Yields - > to be plotted - > select on schematic". That will bring your inverter cell see window in front. Select

hub voltages by tapping on the net. We will tap on information and yield nets (wires) to choose information and yield voltages. The flows can be chosen by tapping on the terminals (red squares).

Fig.9 CMOS With Pin, Gnd And Supply(VDD)

## 5. CONCLUSION

The Synchronization of FIFO pointers into the contrary clock area is securely cultivated utilizing Gray code pointers. Producing the FIFO-full status is maybe the hardest piece of a FIFO structure. Double n-bit Gray code counters are important to synchronize and n-bit pointer into the contrary clock area and to utilize a (n-1)- piece pointer to do "full" examination. Synchronizing parallel FIFO pointers utilizing strategies portrayed in area 7.0 is another commendable method to utilize while doing FIFO structure. Creating the FIFO-void status is effortlessly practiced by contrasting equivalent the n-bit read pointer to the synchronized n-bit compose pointer. The methods portrayed in this paper should work with nonconcurrent timekeepers crossing little to huge contrasts in speed. Cautious apportioning of the FIFO modules along clock limits with all yields enrolled can encourage blend and static planning investigation inside the two nonconcurrent clock areas.

## 6. REFERENCES

- [1] Kittur, Harish M. "FIFO Content Addressable Memory-Early Predict And Termiinate Precharge Of Match-Line." IEEE Transactions On Very Large Scale Integration (VLSI) Systems 25.1 (2017).

- [2] Pagiamtzis, Kostas, And Ali Sheikholeslami. "Content-Addressable Memory (CAM) Circuits And Models: An Instructional Exercise And Overview." IEEE Journal Of Solid-State Circuits 41.3 (2006): 712-727.

- [3] Maurya, Satendra Kumar, And Lawrence T. Clark, "A Unique Longest Prefix Coordinating Substance Addressable FIFO Memory For IP Steering." IEEE Transactions On Very Large Scale Integration (VLSI) Systems 19.6 (2011): 963-972.

- [4] S. I. Ali And M. S. Islam, "A Match Line Dynamic Vitality Decrease Strategy For Fast Ternary CAM Utilizing Double Input Sense Intensifier," Microelectron. J., Vol. 45, No. 1, pp. 95-101, Jan. 2014.

- [5] H. Jarollahi, V. Gripon, N. Onizawa, And W. J. Net, "FIFO Algorithm And Design For A Low-Power Content- Addressable Memory Dependent On Meager Grouped Systems," IEEE Trans. Exceptionally Large Scale Integer. (VLSI) Syst., Vol. 23, No. 4, pp. 642-653, Apr. 2015.

- [6] S. J. Ruan, C. Y. Wu, And J. Y. Hsieh, "Low Force Structure Of Precomputation-Based Substance Addressable Memory," IEEE Trans. Large Scale Integer. (VLSI) Syst., Vol. 16, No. 3,pp. 331-335, Mar. 2008.

- [7] Chang, Yen-Jen, And Yuan-Hong Liao. "FIFO Hybrid-Type Structure For Both Force And Execution Proficiency." IEEE Transactions On Very Large Scale Integration (VLSI) Systems 16.8 (2008): 965-974.