# DESIGN AND PERFORMNCE ANALYSIS OF LOW DENSITY PARITY CHECK ENCODER AND DECODER

<sup>1</sup>Vijaya Kiran G, <sup>1</sup>D Jayanayudu, <sup>2</sup>D K Kavitha, <sup>3</sup>Yelithoti Sravana Kumar <sup>1</sup>Department of ECE, Siddartha Institute of Science and Technology, Puttur, A.P, INDIA. <sup>2</sup>Department of ECE, Pace institute of Technology and sciences, Ongole, A.P, INDIA. <sup>3</sup>Department of ECE, SVP Engineering College, Visakhapatnam, A.P, INDIA

## ABSTRACT:

Here it proposes new low-density parity-check (LDPC) encoder architecture and a parallel low-density parity-check (LDPC) decoding algorithm on GPUs. In this paper the basic construction of effective LDPC parity matrix is transformed in to parallel encoding operations of rows and columns. An optimized method for controlling memories is also proposed which can be reused with different code rates which enhance the use of components assets. Then the planned LDPC encoder along with decoders is designed with Xilinx FPGA software. Confer into Modelsim's results, it can again authenticated that the proposed technique is advantageous by less assets usage, less required power and also precision is high. Then proposed encoders and decoders brings in a throughput of 400 Mbps. Among the test data transmission with Lena base binary images this paper presents a effective design and implementation for LDPC decoder, dedicated application specific integrated circuit (ASIC) or field-programmable gate array (FPGA) constructions into later years to support huge performance given their lengthy deployment period, huge level construction along with particularly rigid functionality. Any other way, effective software system constructions on GPU provide versatile, expandable, and low cost solution in shorter deployment periods. This can acquire high throughput in computerized correspondence frameworks, it presents minimum GPU-based advancements about major LDPC decoder algorithms.

KEY WORDS: LDPC Encoder, LDPC Decoder, GPU, ASIC, FPGA

# 1. INTRODUCTION:

Contrasted with traditional analog broadcasting system, digital audio broadcasting (DAB) system enjoys superior reception quality, stronger anti-interference ability, wider coverage and higher spectrum efficiency, which is more suitable for high-speed mobile reception [1]. The three fundamental specialized plans of DAB frameworks were DABEureka-147, DRM/DRM+, and HD Radio IBOC framework [1-2].

The Administration of State Radio Films and Television discharged rules about DAB Systems in 2006 year in China. It is to be that as it may, can't broadly deployed in China on account of issues, for example, guideline, patent, similarity, etc. In 2013, the SARFT officially discharged the most recent DAB rules in Band-Part1 Frequency Modulation (FM) including Channel Coding, Framing Structure, along with Modulations.

Those standards are called Chinese Digital Radio like as DAB standards that actualize transmit within increasingly strong range along best code calculation [3–5]. Then the Chinese Digital Radio ought to apply all through the country. Thus, planning and upgrading effective Chinese Digital Radio models, that has extraordinary down to earth hugeness, is huge.

Effective significant automations by the Chinese Digital Radio Baseband transmissions method is channel coding. The LDPC coding, as an advanced channel coding technique, havingquality of correctcrack errors along minimum error level stage, cannotcompelling interlacing of subcarriers. Several advancement into the theoretical bound by LDPC explained here over the past few years, along with the theories [1-3], simulations [4], and [5] along with designs [6]–[8]. When compared to traditional cascaded channelcoding the LDPC coding were their simple for hardware implementation. The encoder cost for the LDPC codes is low which makes the LDPC codes more efficient when compare hardware cost.

#### 1.2. LDPC ENCODING ALGORITHM

Then structure matrix into CDR standards LDPC codecan't divide into quid-cycle matrixes blocks. In,parallel decode endures about higher LDPC codinginto achieve huge decode through the basis of that can have equal palled alterinto design effective LDPC coding encoders about all CDR standard code rates. Let  $m=\{m0,m1,\cdots,mi,\cdots,mk-1\}$  being that informative sequences being encode,  $mi=\{mi,0,mi,1,\cdots,mi,b-1\}$ , for  $0\le i\le k-1$ . That is, the information sequence m is divided to k number of groups, along every have elongation about k bits.

$$s=m\times G=\{m0,m1,\cdots,mk-1,p0,p1,\cdots,pc-1\}....(1)$$

Where, p<sub>i</sub> denoted checking of parity bits:

$$pj = \{pj, 0, pj, 1, \dots, pj, b-1\}, 0 \le j \le c-1, \dots (2)$$

computed by

$$pj = \{m0G0, j+m1G1, j+\cdots+mk-1Gk-1, j\}...$$

(3)

Let g(0) i,j = {g(b) i,j = gi,j, g(l) i,j} denotes that results about generators polynomial gi, j rotating l bits to right shift . That can

mi Gi, j =mi,0g(0) i, j +mi,1g(1) i, j +

$$\cdots$$

+mi,b-1g(b-1) i, j ......(4)

## 1.2 LDPC DECODING ALGORITHM

Checking of parity (LDPC) low-density coding is classes aboutlineage blocks. The names derived againstcheckingparity matrix featured, that includes a little 1's as opposed into that numbers by 0's. Our key benefit is that they have an efficiency that is very similar to decoding capabilities for several different channels and linear time-complex algorithms.

LDPC decoding involves message transmission between connected nodes, as indicated in the Tanner graph. Inside a Tanner table, those two gatherings about hubs were denoted Bit Nodes along Checking Nodes. Leather treated diagrams having demonstrated into effective derivation computation calculations, along the utilization into numerous applications. The LDPC coding is being direct (n; k) square code characterized of scanty parallel equality check H lattices about measurement m x n, within m = n-k along rate = k/n. The equality checking H framework of IEEE802 system.

## II. IMPLEMENTATION

#### 2.1. LDPC ENCODER SYSTEM:

Checking of parity code is used to correct info errors in Chinese Digital Radio's main business info system. Then developingforge on the given parity forge is to be calculated of blocking the Gaussian destruction method. As stated earlier, the resulting generator matrix can be divided into design  $256 \times 256$  sub-blocks along every sub divide-forge that circulating features is boost code effectiveness.

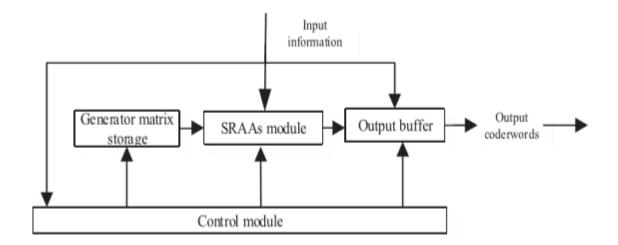

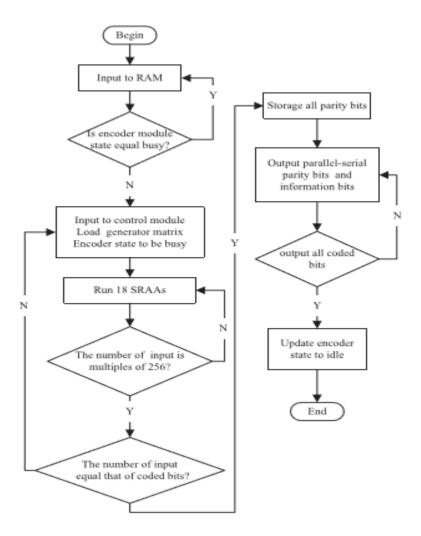

Figure 1: construction of the LDPC coding based by Chinese Digital Radio.

Figure 1 presents effective by Chinese Digital Radio's based LDPC construction figure. The parity checkencoder in this paper occupies double-node Random Access Memory into perform read along write. By gradually increasing RAM used to general controlled which will be initializing that address and read/write operations conferinto those contrasting levels of coding. Fig. 1 explains thataccurate encoding processing about rate 1/2 parity check coding with informative lengths 4608 bit. Next, insert that bit of information in that RAM cushion along test if that state of the encode modules are engage. Once the encode modules are own, then control of input modules for knowledge bits, that begins loading this polynomial creator along adjusting that busy states of the encoder. We can observe that 18thRegister ShiftingAccumulator Adder (RSAA) circuit's module is working into paralleling with the encoder. The equality bit which were being produced are put away in storage subsequent to getting each and every edge containing data bits, with corresponding to sequential change. The encoder yield contains the data bits first and yields equality bit. Then

encoder stage will be changing from occupied to sit when a solitary casing of information encoding is finished. It can list fallows the all modules.

Figure 2. The controlled algorithm about to rate LDPC encoder system.

### 2.2. LDPC DECODING:

The proposal decoder system architecture can explain in those following sections. The Minimum Summation structure precedingthe class of decoding algorithms used to decode the LDPC code is collected called the data movement algorithm because it can describe the process by passing messages along the edges of the Tanner graph. Through Tanner, the graphic nodes operate in isolation, accessing only the information in the messages of the connected edges. The message passing algorithm is also called an iterative decoding algorithm because the message loops back and forth between the bit nodes and the verification nodes until the result is reached (or the process stops). Different message passing algorithms are named, depending on the type of message passed or the type of operation performed on the node.

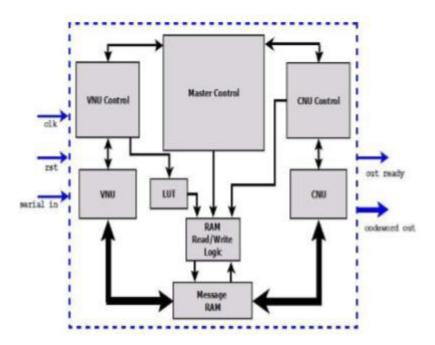

Figure 3: LDPC decoder architecture.

Multiplexed memory is used by the decoder in order to store the check messages and the node variable. The approach reduces FPGA resource consumption. The test nodes will work by reading memory messages directly and retrieving computed messages. The decoder stores the test messages and the node variable using a multiplexed memory. The solution eliminates the usage of FPGA tools. The test nodes must work by directly reading memory messages and retrieving computed messages.

# III. SIMULATION RESULTS

# 3.1. LDPC Encoder:

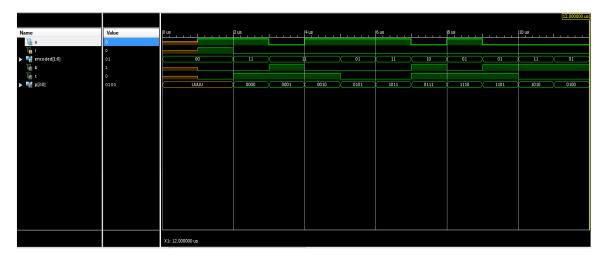

Hare the MATLAB-based encoder is implemented, which is simulation results about the encode endures verify aboutrate by Self HT, with C being the word output. Second, Modelsim platform generated random bit is input into Matlab along with proposalencoder system. Eventually, when compare that outcomes of simulations has done in mat lab, it can find that that both tests is similar. Hence effective LDPC encoder system modules are correctly designed within that encode concept.

Figure 4: Simulation results of LDPC Encoder system

## 3.2. LDPC Decoder:

The proposed LDPC decoder was implemented in Spartan-6 FPGA as a synthesizable Verilog HDL model. To generate the decoder input data, a MATLAB program was written down. Synthesized module simulations were made using the Xilinx ISIM simulator. The units of the test node and variable node were checked by independent simulations of the two systems. Simulations for the modules were performed by writing test bench programs. Figures display the product of the test node unit and variable node unit simulation.

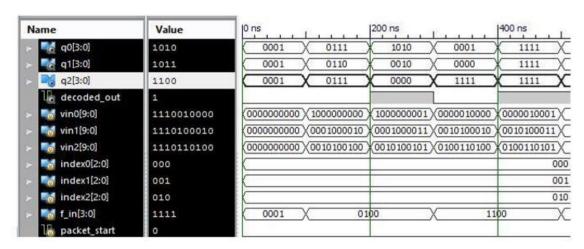

Figure 5: variable node function simulation results

The proposed CNU and VNU designs can be seen to be using fewer hardware resources. This is achieved by adopting the min-sum decoding algorithm, which is simpler compared to other decoding algorithms. But that reduction in the complexity of decoding comes at the expense of reduced performance. Analysis of the pacing was performed using Xilinx Pacing Analyser. The report on timing shows the maximum possible.

# IV. CONCLUSION

This conclusions are gives the low-thickness equality check decoder execution with an altered check hub along variable hub structures. That new check hub configuration makes up for the presentation misfortune acquired in the ordinary min-aggregate calculation. Then variable hub design introduced in this paper diminishes the flood mistake during the control of 4-piece quantized hub messages. Likewise, the new engineering outcomes in diminished equipment asset utilization.

# **REFERENCES**

- [1] Wang Yongqing, Liu Donglei, Sun Lida and Wu Siliang, "Real-Time Implementation for Reduced-Complexity LDPC Decoder in Satellite Communication," China Communications, December 2014.

- [2] Peter Hailes, Lei Xu, Robert G. Maunder, Bashir M. Al-Hashimi and LajosHanzo, "A Survey of FPGA-Based LDPC Decoders," IEEE Communications Surveys, Vol. 18, No. 2, Second Quarter 2016.

- [3] Youn Sung Park, Yaoyu Tao, IEEE and Zhengya Zhang, "A Fully Parallel Nonbinary LDPC Decoder With Fine-Grained Dynamic Clock Gating," IEEE Journal of Solid State Circuits, Vol. 50, No. 2, February 2015.

- [4] Bertrand Le Gal, Christophe Jego and Camille Leroux, "A Flexible NISC-Based LDPC Decoder," IEEE Transactions on Signal Processing, Vol. 62, No. 10, May 2014.

- [5] Kai Zhang, Xinming Huang and Zhongfeng Wang, "High-Throughput Layered Decoder Implementation for Quasi-Cyclic LDPC Codes," IEEE Journal on Selected Areas in Communication, Vol. 27, No. 6, August 2009.

- [6] Guido Masera, Federico Quaglio and Fabrizio Vacca, "Implementation of a Flexible LDPC Decoder," IEEE Transactions On Circuits and Systems-II: Express Briefs, Vol. 54, No. 6, June 2007.

- [7] W. C. Huffman and V. Pless, "Fundamentals of Error Correcting Codes," Cambridge University Press, Cambridge UK, 2003.

- [8] W. K. Leung, W. L. Lee, Angus Wu and Li Ping, "Efficient Implementation Technique of LDPC Decoder," IEE Electronic Letters, Vol. 37, No. 20, September 2001.

- [9] R. G. Gallager, "Low-Density Parity-Check Codes", IRE Transactions on Information Theory, Vol. 8, No. 12, January 1962.

- [10] R. M. Tanner, "A Recursive Approach to Low Complexity Codes," IEEE Transactions on Information Theory, Vol. 27, No. 5, September 1981.

- [11] C. E. Shannon, "Certain Results in Coding Theory for Noisy Channels," Information and Control, Vol. 1, September 1951.

- [12] Sheryl L. Howard, Christian Schlegel and Vincent C. Gaudet, "DegreeMatched Check Node Decoding for Regular and Irregular LDPCs," IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 53, No. 10, October 2006.

- [13] Saied Hemati, François Leduc-Primeau and Warren J. Gross, "A Relaxed Min-Sum LDPC Decoder With Simplified Check Nodes," IEEE Communications Letters, Vol. 20, No. 3, March 2016.

- [14] P. Gao, G. Wan, and S. Chen, "Research works and test results of digital radio," in Proc. Int. Coverage Transmiss. Conf., Xi'an, China, 2011, pp. 155–158.

- [15] J. Li, N. Di, P. Gao, G. Sheng, and Z. Wu, "A digital audio broadcasting system using short length QC-LDPC," in Proc. IEEE ICCT, Chengdu, China, Dec. 2012, pp. 1057–1061.

- [16] F. Guo and T. Wang, "The experiment performance of frequency modulation-China digital radio," Radio Television Inf., vol. 40, no. 16, pp. 44–48, Apr. 2014.

- [17] Digital Radio Mondiale System Specification, document ETSI ES 201 980 V3.1.1, Jun. 2009.

- [18] Digital Audio Broad casting in FMB and Part1: Framing Structure Channel Coding and Modulation for Digital Broadcasting Channel, Radio, Film and Television Industry Standard, China, Aug. 2013. [Online]. Available: http://www.chinesestandard.net

- [19] J.Andrade, G.Falcao, V.Silva, and L.Sousa, "A survey on programmable LDPC decoders," IEEE Access, vol. 4, pp. 6704–6718, 2016.

- [20] Q. Huang, L. Tang, S. He, Z. Xiong, and Z. Wang, "Low-complexity encoding of quasicyclic codes based on Galois Fourier transform," IEEE Trans. Commun., vol. 62, no. 6, pp. 1757–1767, Jun. 2014.